NXP PMIC Solution for MediaTek MT2712 Processors Rev. 1 — 24 June 2021 Applie

**Application note**

#### **Document information**

| Information | Content                                                                                                                                                                                                                                                              |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Keywords    | FS56, PF81, PF5024, Power solution, PMIC, MediaTek MT2712, Infotaiment, Functional safety                                                                                                                                                                            |

| Abstract    | NXP's Power Management IC (PMIC) integrates multiple power supply<br>channels and is suitable for high-performance In-Vehicle Infotainment (IVI)<br>systems. This application note describes NXP's PMIC solution for MediaTek<br>MT2712 processor-based IVI systems. |

## **Revision History**

#### Table 1. Revision history

| Revision      | Date     | Description     |

|---------------|----------|-----------------|

| AN13247 v.1   | 20210624 | Initial Release |

| Modifications | NA       | -<br>-          |

## **1** Introduction

This application note describes how NXP Power Management ICs (PMIC), which feature power tree configuration, power-up and power-down sequences, and digital control, can be implemented in systems that use a MediaTek MT2712 processor. This document also highlights the safety mechanisms embedded in the PMIC and includes information on interconnecting NXP functional safety PMICs with MT2712-based systems that have safety requirements.

In addition, the document also provides schematics and a BOM for a typical NXP PMIC/ MT2712 power solution.

## 2 System Design

The MT2712 is a MediaTek processor designed for in-vehicle infotainment (IVI) systems. The device consists of a high-performance, hexa-core system-on-chip (SoC) that features multiple ARM Cortex cores integrated in a single device. NXP's PMICs provides an ideal solution with a 1\*PF81 and 1\*PF5024 to power MT2712 processor systems. The PF8100 and PD5024 are highly-integrate multiple regulators well-suited to accommodate the high-performance demands of IVI processors like the MT2712.

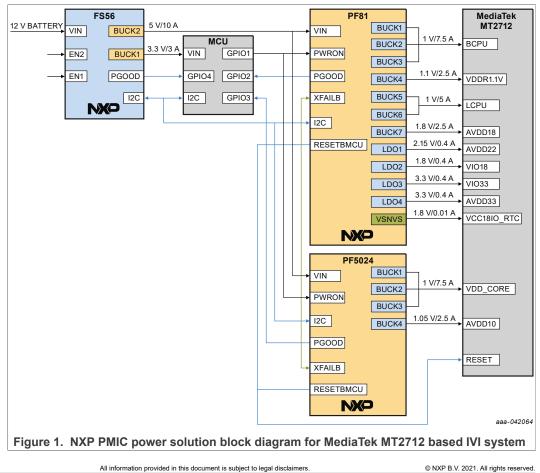

<u>Figure 1</u> shows the NXP PMIC power solution for MT2712-based IVI system. The block diagram is based on a Quality Management (QM) PMIC for systems with QM requirements. Normally, a single MCU is linked with the MT2712 for IVI applications. One function of the MCU is to control the MT2712's domain power on/off function.

The FS56 is an automotive multi-output power supply integrated circuit. It has a batteryconnected pre-regulator Buck2 that generates intermediate voltages to supply power to the PF81 and F5024. The FS56 also integrates a battery connected Buck1 regulator that can be used to supply the MCU and other peripherals. The FS56 supports 12 V battery systems. The PF81 and PF5024 provide regulators for the MT2712's power rails.

The FS56, PF81, PF5024 feature a built-in one-time programmable (OTP) memory that stores key startup configurations. The PF81 and the PF5024 also have dedicated functional blocks for synchronizing multiple PMIC operations. These blocks minimize design time and reduce system complexity by implementing a single-chipset approach that eliminates the need for external controllers to support system default voltage configurations and power up synchronization.

| PMIC   | Block                                                                        | Functions                                                                                    |

|--------|------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

|        | Vin                                                                          | Power input from 12 V battery                                                                |

|        | Buck1, Buck2                                                                 | Power supply output                                                                          |

|        | EN1                                                                          | Enable signal for Buck2; connects to KL15 or CAN transceiver INH signal                      |

| FS56   | EN2                                                                          | Enable signal for Buck2; connect to 12 V battery if FS56 Buck2 needs always-on functionality |

|        | Pgood                                                                        | PF81 Power good indicator                                                                    |

|        | l <sup>2</sup> C                                                             | I <sup>2</sup> C communication with MCU                                                      |

|        | Vin                                                                          | Power input from FS56                                                                        |

|        | Buck1, Buck2 ,Buck3, Buck4, Buck5,<br>Buck6, Buck7<br>LDO1, LDO2, LDO3, LDO4 | Power supply output                                                                          |

|        | VSNVS                                                                        | Always-on power supply for MT2712 RTC                                                        |

|        | POWERON                                                                      | PF81 power-up enable input controlled by MCU                                                 |

| PF81   | l <sup>2</sup> C                                                             | I <sup>2</sup> C communication with MCU                                                      |

|        | Pgood                                                                        | PF81 Power good indicator                                                                    |

|        | XFAILB                                                                       | Bidirectional pin for multi PMIC power-up\down sequence synchronization                      |

|        | RESETMCU                                                                     | Reset connection wtih MT2712                                                                 |

|        | Vin                                                                          | Power input from FS56                                                                        |

|        | Buck1, Buck2, Buck3, Buck4                                                   | PF5024 Power supply output                                                                   |

| PF5024 | POWERON                                                                      | PF5024 power-up enable input which control by MCU                                            |

|        | l <sup>2</sup> C                                                             | I <sup>2</sup> C communication with MCU                                                      |

|        | Pgood                                                                        | PF5024 Power good indicator                                                                  |

|        | XFAILB                                                                       | Bidirectional pin for multi pmic power up\down sequence synchronization                      |

|        | RESETMCU                                                                     | Reset connection wtih MT2712                                                                 |

## 3 MT2712 Power Solution

The PF81 contains seven high-efficiency buck converters and four linear regulators with load switch options. The PF5024 contains four buck converters. Each buck converter on both the PF81 and the PF5024 are rated up to 2500 mA and linear regulator rated up to 400 mA. PF81 and PF5024 buck converters support Dynamic Voltage Scaling (DVS). For an MT2712 power solution, PF PMICs input voltage is supplied from the FS56 BUCK2 output.

| PMIC   | Power<br>Channel | Output<br>Voltage/V | Current<br>Capability/mA | MT2712<br>Power rails | Current<br>Requirement/mA | Power up<br>sequence | Power<br>down<br>sequence |

|--------|------------------|---------------------|--------------------------|-----------------------|---------------------------|----------------------|---------------------------|

| PF81   | Buck1-3          | 1                   | 7500                     | BCPU                  | 7000                      | 2                    | 5                         |

|        | Buck4            | 1.1                 | 2500                     | VDDR1.1V              | 493                       | 6                    | 2                         |

|        | Buck5-6          | 1                   | 5000                     | LCPU                  | 3670                      | 2                    | 5                         |

|        | Buck7            | 1.8                 | 2500                     | AVDD18                | 1490                      | 4                    | 3                         |

|        | LDO1             | 2.15                | 400                      | AVDD22                | 4                         | 3                    | 4                         |

|        | LDO2             | 1.8                 | 400                      | VIO18                 | 20                        | 4                    | 3                         |

|        | LDO3             | 3.3                 | 400                      | VIO33                 | 75                        | 5                    | 2                         |

|        | LDO4             | 3.3                 | 400                      | AVDD33                | 12                        | 5                    | 2                         |

|        | VSNVS            | 1.8                 | 10                       | VCC18IO_RTC           | 0.03                      | 1                    | —                         |

| PF5024 | Buck1-3          | 1                   | 7500                     | VDD_CORE              | 6750                      | 2                    | 5                         |

|        | Buck4            | 1.05                | 2500                     | AVDD10                | 60                        | 4                    | 3                         |

|        | RESETBMCU        |                     | _                        | nRESET                | —                         | 7                    | 1                         |

Table 3. MT2712 power rails requirements and PMIC output configuration

## **NXP Semiconductors**

# AN13247

## NXP PMIC Solution for MediaTek MT2712 Processors

| FS56 VIN _/                                                         |                |

|---------------------------------------------------------------------|----------------|

| FS56 EN1 and EN2                                                    | FS56           |

| FS56 Buck1 and Buck2                                                |                |

| FS56 PGOOD MCU GPIO                                                 |                |

| PF81, PF5024 PWRON                                                  | PF81, P        |

| PF81, PF5024 XFAIL                                                  | PF81,          |

| → ← Fuse load → ← 2 ms                                              | PF81 VSNVS     |

| F81 Buck1-3 BCPU                                                    | PF81 Buck1-3   |

| F81 Buck5-6 LCPU                                                    | PF81 Buck5-6   |

|                                                                     | PF5024 Buck1-3 |

| PF81 LD01 AVDD22                                                    | PF81 LDO1      |

| → → 2 ms → → 2 ms                                                   | PF81 LDO2      |

| PF81 Buck7 AVDD18                                                   | PF81 Buck7     |

|                                                                     | PF5024 Buck4   |

| PF82 LD03 VI033                                                     | PF82 LDO3      |

| PF82 LD04 AVDD33                                                    | PF82 LDO4      |

| PF81 Buck4 VDDR1.1V                                                 | PF81 Buck4     |

| RESETBMCU                                                           |                |

| aaa-042068                                                          |                |

| igure 2. MediaTek MT2712 processor power-up and power-down sequence | Figure 2.      |

Through the internal power-up sequencer (PWRON, XFAILB) function available on all NXP PMICs, the PF81 and the PF5024 effectively implement accurate power-up and power-down sequence synchronization for all power rails. The default sequence slots for PMICs are programmed via the OTP configuration registers. Figure 2 illustrates MT2712 processor power-up and down sequence. The specific power sequence configuration for MT2712 are programmed by OTP registers. When VIN on the PF81 or the PF5024 exceeds the UVDET threshold and the PMICs complete loading the fused configuration, VSNVS powers up. When PWRON is pulled high, the PMICs start the power-up process. PMIC regulators automatically power up according to the power-up sequence configured in the OTP. When RESETBMCU is released, the power-up sequence is complete and the MT2712 boots up.

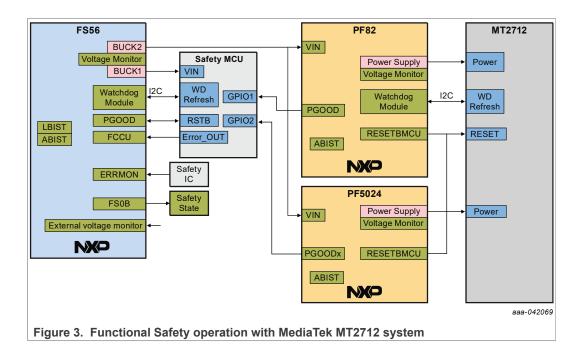

## 4 Functional Safety

For safety applications with functional safety requirements, NXP provides ASIL-B and ASIL-D versions that are pin-to-pin compatible with the QM versions. The FS56, PF81, and PF5024 are ASIL-B PMIC versions with embedded safety mechanisms that comply with ISO26262. These safety mechanisms include:

- **Voltage monitoring**: NXP PMICs feature an independent voltage monitoring function for each regulator. The PMIC fault-monitoring block monitors UV, OV and ILIM faults and indicates the output state of each regulator through the PGOODx voltage regulation status pins.

- Watchdog monitoring: The PF81 features internal watchdog timers capable of monitoring the MT2712 processor. The FS56 also has watchdog timers capable of monitoring a safety MCU. If the PMIC internal watchdog times out, the PMIC initiates a reset.

- I<sup>2</sup>C CRC and write protection: The PMICs have functional I<sup>2</sup>C registers that are fuseconfigurable. The fuse circuits have CRC error checking routines that report on and protect against PMIC register loading errors. If a register loading error is detected, a corresponding error flag is asserted. An I<sup>2</sup>C secure-write protects secure registers from an invalid operation.

- Analog built-in self-test(ABIST): ABIST is designed to diagnose latent faults. It checks the voltage monitoring block (OV/UV) of each regulator to determine whether a fault has occurred. If a failure on the OV/UV monitor is detected, the PMIC asserts the corresponding ABIST flags in the I<sup>2</sup>C register.

- **Functional safety output:** The FS56 has a functional safety output FSOB that transitions the system into a safe state when a fault cannot be handled by the safety MCU.

- VIN OVLO function: The PF82 and PF5024 feature VIN\_OVLO circuits that monitor the PMIC's main input supply. The PMIC monitors its input voltage and initiates a power-down sequence when it detects a VIN\_OVLO in the system.

- MCU failure monitoring (FS56 only): The FS56 ASIL-B version features an FCCU function in charge of monitoring hardware failures from the MCU. The FCCU pins are connected to the fault output pins of the MCU. When the FCCU pin indicates that an MCU fault has occurred, the FS56 resets the MCU and\or asserts the FSOB pin.

- External IC monitoring (FS56 only): The FS56 features an ERRMON function that monitors external safety IC faults in the application.

- External voltage monitor (FS56 only): The FS56 ASIL-B part supports up to 4x VMON. Depending on the safety requirements, VMON can be used to monitor the PF82 to assure that the device maintains the required safety level for the system.

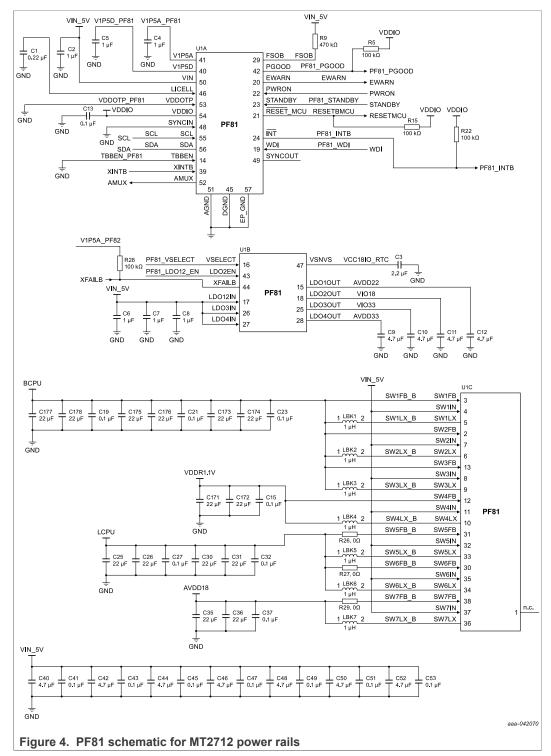

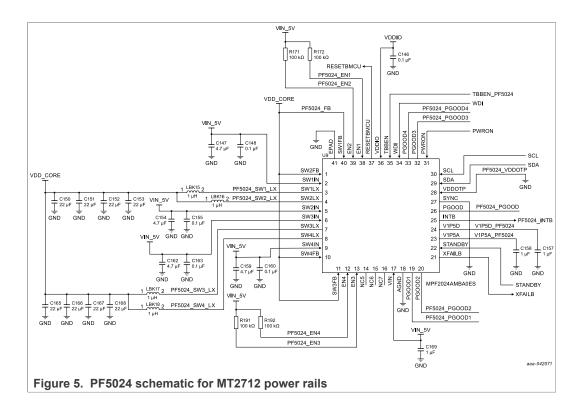

## **5** Schematic

Figure 4 and Figure 5 show an MT2712 processor power solution schematic based on NXP PMICs.

NXP PMIC Solution for MediaTek MT2712 Processors

## 6 Bill of Material

<u>Table 4</u> provides a list of the recommended components for the NXP PMIC/MT2712 power solution defined in <u>Section 5 "Schematic"</u>. The components listed here are shown with representative part numbers; they can be substituted with equivalent parts.

#### Table 4. Bill of Materials

| Value   | Qty | Part Number          | Description         | Vendor | Component                  |

|---------|-----|----------------------|---------------------|--------|----------------------------|

|         | 1   | PF81                 | Power management IC | NXP    | PMIC                       |

|         | 1   | PF5024               | Power management IC | NXP    | PMIC                       |

| 0.22 µF | 1   | GRT155C81E224KE01    | 25 V 10% X6S 0402   | MURATA | Output capacitor           |

| 1.0 µF  | 9   | GCM155C71A105KE38D   | 10 V 10% X7S 0402   | MURATA | Input capacitor            |

| 2.2 µF  | 1   | GRT155C71A225KE13    | 10 V 10% X7S 0402   | MURATA | Output capacitor           |

| 4.7 µF  | 15  | GRT188C81E475KE13    | 25 V 10% X6S 0603   | MURATA | Output capacitor           |

| 0.1 µF  | 20  | GCM155R71C104KA55D   | 16 V 10% X7R 0402   | MURATA | Input and Output capacitor |

| 22 µF   | 22  | GRT21BC81A226ME13    | 10 V 20% X6S 0805   | MURATA | Output capacitor           |

| 1.0 µH  | 14  | TFM252012ALMA1R0MTAA | 4.7 A 20% SMD       | TDK    | Output inductor            |

## 7 Reference Resource

#### PF5024

- [1] PF5024 Data Sheet and Application Note

- [2] OTP configuration tool and Flex GUI

- [3] EVM board PCB and schematic

#### PF8100-PF8200

- [4] PF8100-PF8200 Documentation (Data Sheet, Application Notes, Errata, etc.)

- [5] OTP configuration tool and Flex GUI

- [6] EVM board PCB and schematic

#### PF56

[7] Contact and NXP sales representative or FAE to apply for documents and samples

#### General

[8] Power Management community

#### NXP PMIC Solution for MediaTek MT2712 Processors

## 8 Legal information

## 8.1 Definitions

**Draft** — A draft status on a document indicates that the content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included in a draft version of a document and shall have no liability for the consequences of use of such information.

## 8.2 Disclaimers

Limited warranty and liability - Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. NXP Semiconductors takes no responsibility for the content in this document if provided by an information source outside of NXP Semiconductors. In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory. Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Terms and conditions of commercial sale of NXP Semiconductors.

**Right to make changes** — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Suitability for use — NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors and its suppliers accept no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

Applications — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification. Customers are responsible for the design and operation of their applications and products using NXP Semiconductors products, and NXP Semiconductors accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the NXP Semiconductors product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products. NXP Semiconductors does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using NXP Semiconductors products in order to avoid a default of the applications and the products or of the application or use by

customer's third party customer(s). NXP does not accept any liability in this respect.

Terms and conditions of commercial sale — NXP Semiconductors products are sold subject to the general terms and conditions of commercial sale, as published at http://www.nxp.com/profile/terms, unless otherwise agreed in a valid written individual agreement. In case an individual agreement is concluded only the terms and conditions of the respective agreement shall apply. NXP Semiconductors hereby expressly objects to applying the customer's general terms and conditions with regard to the purchase of NXP Semiconductors products by customer.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.

Evaluation products — This product is provided on an "as is" and "with all faults" basis for evaluation purposes only. NXP Semiconductors, its affiliates and their suppliers expressly disclaim all warranties, whether express, implied or statutory, including but not limited to the implied warranties of non-infringement, merchantability and fitness for a particular purpose. The entire risk as to the quality, or arising out of the use or performance, of this product remains with customer. In no event shall NXP Semiconductors, its affiliates or their suppliers be liable to customer for any special, indirect, consequential, punitive or incidental damages (including without limitation damages for loss of business, business interruption, loss of use, loss of data or information, and the like) arising out the use of or inability to use the product, whether or not based on tort (including negligence), strict liability, breach of contract, breach of warranty or any other theory, even if advised of the possibility of such damages. Notwithstanding any damages that customer might incur for any reason whatsoever (including without limitation, all damages referenced above and all direct or general damages), the entire liability of NXP Semiconductors, its affiliates and their suppliers and customer's exclusive remedy for all of the foregoing shall be limited to actual damages incurred by customer based on reasonable reliance up to the greater of the amount actually paid by customer for the product or five dollars (US\$5.00). The foregoing limitations, exclusions and disclaimers shall apply to the maximum extent permitted by applicable law, even if any remedy fails of its essential purpose.

**Translations** — A non-English (translated) version of a document is for reference only. The English version shall prevail in case of any discrepancy between the translated and English versions.

- Customer understands that all NXP products may be subject Security to unidentified or documented vulnerabilities. Customer is responsible for the design and operation of its applications and products throughout their lifecycles to reduce the effect of these vulnerabilities on customer's applications and products. Customer's responsibility also extends to other open and/or proprietary technologies supported by NXP products for use in customer's applications. NXP accepts no liability for any vulnerability. Customer should regularly check security updates from NXP and follow up appropriately. Customer shall select products with security features that best meet rules, regulations, and standards of the intended application and make the ultimate design decisions regarding its products and is solely responsible for compliance with all legal, regulatory, and security related requirements concerning its products, regardless of any information or support that may be provided by NXP. NXP has a Product Security Incident Response Team (PSIRT) (reachable at PSIRT@nxp.com) that manages the investigation, reporting, and solution release to security vulnerabilities of NXP products.

## 8.3 Trademarks

Notice: All referenced brands, product names, service names and trademarks are the property of their respective owners.

NXP — wordmark and logo are trademarks of NXP B.V.

### NXP PMIC Solution for MediaTek MT2712 Processors

## **Tables**

| Tab. 1. | Revision history2     |

|---------|-----------------------|

| Tab. 2. | PMIC block functions5 |

| Tab. 3. | MT2712 power rails requirements and |

|---------|-------------------------------------|

|         | PMIC output configuration6          |

| Tab. 4. | Bill of Materials12                 |

## **Figures**

| Fig. 1. | NXP PMIC power solution block diagram  |  |

|---------|----------------------------------------|--|

|         | for MediaTek MT2712 based IVI system4  |  |

| Fig. 2. | MediaTek MT2712 processor power-up and |  |

|         | power-down sequence7                   |  |

|         | • •                                    |  |

- Fig. 3. Functional Safety operation with MediaTek

- Fig. 4. Fig. 5.

- PF5024 schematic for MT2712 power rails ..... 11

#### NXP PMIC Solution for MediaTek MT2712 Processors

## Contents

| 1 | Introduction          | 3  |

|---|-----------------------|----|

| 2 | System Design         | 4  |

| 3 | MT2712 Power Solution |    |

| 4 | Functional Safety     | 8  |

| 5 | Schematic             | 10 |

| 6 | Bill of Material      |    |

| 7 | Reference Resource    |    |

| 8 | Legal information     |    |

|   |                       |    |

Please be aware that important notices concerning this document and the product(s) described herein, have been included in section 'Legal information'.

#### © NXP B.V. 2021.

All rights reserved.

For more information, please visit: http://www.nxp.com For sales office addresses, please send an email to: salesaddresses@nxp.com

Date of release: 24 June 2021 Document identifier: AN13247