# AN13761 PSI5 programming mode procedures for FXLS9xxxx sensors Rev. 1.1 – 29 November 2023

**Application note**

#### **Document information**

| Information | Content                                                                                                                                                               |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Keywords    | FXLS93xxx, FXLS93xx0, OTP, one time programmable memory, sensor, single channel, dual-<br>channel, inertial sensor, PSI5.                                             |

| Abstract    | AN13761 describes procedures to perform one time programmable (OTP) memory of the FXLS93xxx single and dual- channel inertial sensor using the PSI5 programming mode. |

## 1 Introduction

This document describes the recommended procedures to program the One Time Programmable (OTP) memory of the FXLS93xxx single and dual-channel inertial sensors using PSI5 programming mode. It describes the recommended procedures for initializing and configuring FXLS93xxx devices on a PSI5 bus transmission using PSI5 programming mode.

# 2 Applicable parts

This document applies to the NXP sensors listed in Table 1.

Table 1. Applicable parts

| Part      | Description                         |

|-----------|-------------------------------------|

| FXLS93xxx | Dual-channel PSI5 Inertial Sensor   |

| FXLS93xx0 | Single-channel PSI5 Inertial Sensor |

## **3** Application schematic and device connections

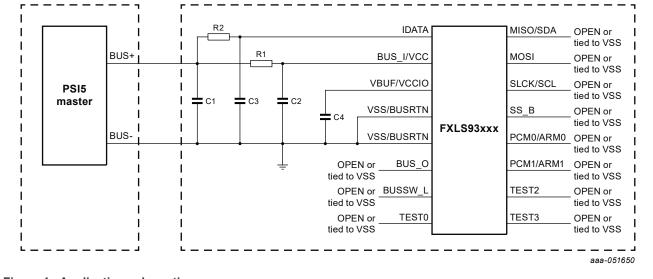

The procedures outlined in this document assume that one sensor is connected to a PSI5 controller. The PSI5 controller provides both power and communication via the BUS\_I and BUSRTN pins through the recommended PSI5 network shown in Figure 1 and Table 2.

Figure 1. Application schematic

. . . . . . . . . . . . . . . .

| Table 2. PSI       | able 2. PSIS OTP Programming of a PSIS application device |                                    |                                                            |  |  |  |  |  |  |  |  |

|--------------------|-----------------------------------------------------------|------------------------------------|------------------------------------------------------------|--|--|--|--|--|--|--|--|

|                    | Recommended Components                                    |                                    |                                                            |  |  |  |  |  |  |  |  |

| Ref.<br>Designator | Туре                                                      | Description                        | Purpose                                                    |  |  |  |  |  |  |  |  |

| C1                 | Ceramic                                                   | 2.2 nF, 10 %,<br>50 V minimum, X7R | V <sub>CC</sub> power supply decoupling and signal damping |  |  |  |  |  |  |  |  |

| C2                 | Ceramic                                                   | 15 nF, 10 %,<br>50 V minimum, X7R  | V <sub>CC</sub> power supply decoupling                    |  |  |  |  |  |  |  |  |

of a DOLE and listing device

|                    | Recommended Components |                                     |                                                          |  |  |  |  |  |  |  |  |

|--------------------|------------------------|-------------------------------------|----------------------------------------------------------|--|--|--|--|--|--|--|--|

| Ref.<br>Designator | Туре                   | Description                         | Purpose                                                  |  |  |  |  |  |  |  |  |

| C3                 | Ceramic                | 470 pF, 10 %,<br>50 V minimum, X7R  | I <sub>DATA</sub> power supply decoupling                |  |  |  |  |  |  |  |  |

| C4                 | Ceramic                | 0.47 µF, 10 %,<br>10 V minimum, X7R | Buffer regulator output capacitor for micro-cut immunity |  |  |  |  |  |  |  |  |

| R1                 | General Purpose        | 82 Ω, 5 %, 200 PPM                  | V <sub>CC</sub> filtering and signal damping             |  |  |  |  |  |  |  |  |

| R1                 | General Purpose        | 27 Ω, 5 %, 200 PPM                  | I <sub>DATA</sub> filtering and signal damping           |  |  |  |  |  |  |  |  |

Table 2. PSI5 OTP Programming of a PSI5 application device...continued

## **4** Device power restrictions

Power must be applied to the FXLS93xxx with the ramp rates specified in the data sheet. The supply voltage for the device is applied through the PSI5 network shown in <u>Figure 1</u>. As specified in the data sheet, the voltage at the IDATA pin during OTP memory programming must be between 9 V and 11 V. The source must be able to supply the full current draw of the bus plus an additional 5 mA without dipping below 9 V. The applied voltage must consider the voltage drop across the PSI5 network resistor, R1 as shown in the equations below:

$$\begin{split} VSUP_{MIN} &\geq BUS\_I_{VPPMIN} + I_{VPP} \times R2_{MAX} \\ VSUP_{MIN} &\geq 9 \ V + (9 \ mA + 5 \ mA) \times 72 \ \Omega = 10.3 \ V \\ VSUP_{MAX} &\leq BUS\_I_{VPPMAX} + I_{VPP} \times R1_{MIN} \\ VSUP_{MAX} &\leq 11 \ V + (4 \ mA) \times 92 \ \Omega = 11.3 \ V \end{split}$$

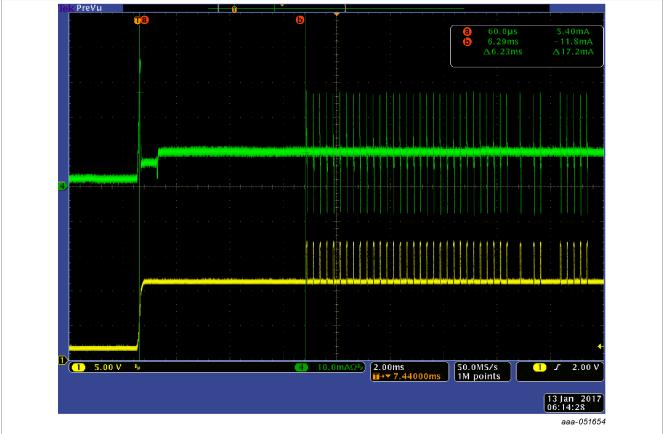

The example in this document uses a supply voltage of 11.0 V with a current limit of 125 mA. The supply ramp is shown in <u>Figure 2</u>.

Figure 2. Programming Voltage Supply Ramp

# 5 Bidirectional communication via PSI5 programming mode

The following sections describe PSI5 Programming Mode and its use to configure, program, and test an FXLS93xxx device. All communication in PSI5 Programming Mode uses the following settings and timing.

| Parameter               | Value              |  |  |  |  |  |  |

|-------------------------|--------------------|--|--|--|--|--|--|

| Sync pulse rate         | 4 kHz (250 μs)     |  |  |  |  |  |  |

| Response time slot      | Time Slot 1: 46 µs |  |  |  |  |  |  |

| Response data size      | 10-bit             |  |  |  |  |  |  |

| Response error checking | Even parity        |  |  |  |  |  |  |

| Response bit rate       | 125 kbit/s (8 μs)  |  |  |  |  |  |  |

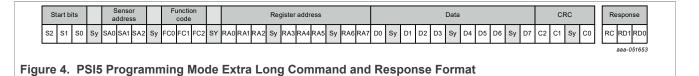

All PSI5 Programming Mode Commands use either the Short or Extra Long format and must include sync bits (logic 1) every fourth bit as shown in <u>Figure 3</u> and <u>Figure 4</u>.

| S  | tart bi | its |    | -   | Sensc<br>ddres | -   |    |     | Function code |     | C  |    | CRC |    | Response |     |

|----|---------|-----|----|-----|----------------|-----|----|-----|---------------|-----|----|----|-----|----|----------|-----|

| S2 | S1      | S0  | Sy | SA0 | SA1            | SA2 | Sy | FC0 | FC1           | FC2 | SY | C2 | C1  | C0 | RC       | RD1 |

aaa-051652

Figure 3. PSI5 Programming Mode Short Command and Response Format

4 / 27

### 5.1 Power on PSI5 programming mode communication delay

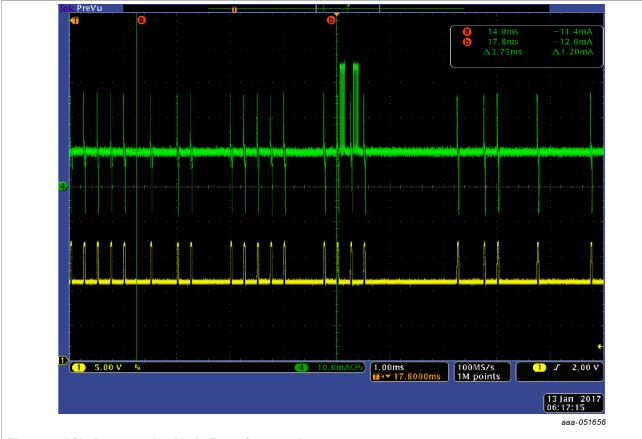

A PSI5 programmed device will decode Programming Mode Entry commands from 6 ms to 133 ms after power is applied to the sensor. The PSI5 controller must provide at least 6 ms prior to sending the PSI5 Programming Mode Entry Start Condition as shown in Figure 5.

Figure 5. Power On PSI5 Programming Mode Communication Delay

## 5.2 PSI5 programming mode entry start condition

Precede the Programming Mode Entry command with a start condition consisting of 31 consecutive logic 1s (sync pulses) as shown in <u>Figure 6</u>.

Figure 6. PSI5 Programming Mode Entry Start Condition, 31 Sync Pulses

### 5.3 PSI5 programming mode entry command

The PSI5 Programming Mode Entry (PME) Command is a short command with the format shown in <u>Figure 3</u> and settings shown in <u>Table 4</u> and <u>Table 5</u>. Figure 7 and Figure 8 show the PSI5 PME command and response.

| Table 4. | PSI5 programming | mode entry command | parameters and values |

|----------|------------------|--------------------|-----------------------|

|----------|------------------|--------------------|-----------------------|

| Parameter             | Value |

|-----------------------|-------|

| Command Type          | Short |

| Start Bits (Start)    | 010   |

| Sensor Address (SAdr) | 001   |

| Function Code (FC)    | 111   |

| CRC (CRC)             | 001   |

#### Table 5. PSI5 programming mode entry settings

| Start | Start Bits |    |    | Senso | or Addı | ress | Function Code |     |     | de  |    | CRC |    |    | Respo | onse |

|-------|------------|----|----|-------|---------|------|---------------|-----|-----|-----|----|-----|----|----|-------|------|

| S2    | S1         | S0 | Sy | SA0   | SA1     | SA2  | Sy            | FC0 | FC1 | FC2 | Sy | C2  | C1 | C0 | RC    | RD1  |

| 0     | 1          | 0  | 1  | 0     | 1       | 0    | 1             | 1   | 1   | 1   | 1  | 0   | 0  | 1  | 1E1   | 0CA  |

AN13761 Application note © 2023 NXP B.V. All rights reserved.

Figure 7. PSI5 Programming Mode Entry Command

Figure 8. PSI5 Programming Mode Entry Response

### 5.4 PSI5 programming mode normal command start condition

Once the PME is received, all PSI5 Programming Commands must be preceded using one of the following start conditions:

- A minimum of 5 consecutive logic '0's (with no sync bits)

- A minimum of 31 consecutive logic '1's (this includes logic '1's transmitted for the previous response)

Figure 9 shows an example start condition with 6 nSync bits.

Figure 9. PSI5 Programming Mode Command Start Condition, 6 nSync Bits

### 5.5 PSI5 programming mode normal commands and responses

All PSI5 Programming Mode commands after the PME use the Extra Long Command Format shown in <u>Figure 4</u>. Only two commands are supported: Register Read and Register Write. <u>Table 6</u> and <u>Table 7</u> show the command settings for the 2 commands. <u>Figure 10</u> and <u>Figure 11</u> show the read and write command and response formats for PSI5 programming mode.

| Parameter             | Value      |

|-----------------------|------------|

| Command Type          | XLONG Read |

| Start Bits (Start)    | 010        |

| Sensor Address (SAdr) | 001        |

| Function Code (FC)    | 000        |

| CRC (CRC)             | Variable   |

| esponse      | R   |    | ۶C | CF |    |    |    |    |    | data | ister | Reg |    |    |    |    |         |         |    | ess     | addr    | gister  | Re |         |         |         |    |         |         |         |    |         |         |         |    | ts | art b | St | Sensor<br>address         Function<br>code         Fegister address         Register data         CRC         Response |

|--------------|-----|----|----|----|----|----|----|----|----|------|-------|-----|----|----|----|----|---------|---------|----|---------|---------|---------|----|---------|---------|---------|----|---------|---------|---------|----|---------|---------|---------|----|----|-------|----|------------------------------------------------------------------------------------------------------------------------|

| RD RD<br>1 2 | RC  | C0 | Sy | C1 | C2 | D7 | Sy | D6 | D5 | D4   | Sy    | D3  | D2 | D1 | Sy | D0 | RA<br>7 | RA<br>6 | Sy | RA<br>5 | RA<br>4 | RA<br>3 | Sy | RA<br>2 | RA<br>1 | RA<br>0 | Sy | FC<br>2 | FC<br>1 | FC<br>0 | Sy | SA<br>2 | SA<br>1 | SA<br>0 | Sy | S0 | S1    | S2 |                                                                                                                        |

| C0 D4        | 1E1 | 1  | 1  | 1  | 1  | 0  | 1  | 0  | 0  | 0    | 1     | 0   | 0  | 0  | 1  | 0  | 0       | 0       | 1  | 0       | 0       | 0       | 1  | 0       | 0       | 0       | 1  | 0       | 0       | 0       | 1  | 0       | 1       | 0       | 1  | 0  | 1     | 0  |                                                                                                                        |

#### Figure 10. PSI5 programming mode read register command and response format

AN13761 Application note

| Parameter             | Value       |

|-----------------------|-------------|

| Command Type          | XLONG Write |

| Start Bits (Start)    | 010         |

| Sensor Address (SAdr) | 001         |

| Function Code (FC)    | 001         |

| CRC (CRC)             | Variable    |

| S2 S1 S0 Sv S |                   |    |         |      |      |         |         |         |    |         |         |         |    |         |         |    |    |    |    | Regi | 3101 | Jata |    |    |    |    |    | 0  | RC |    |     | espor   | 30      |

|---------------|-------------------|----|---------|------|------|---------|---------|---------|----|---------|---------|---------|----|---------|---------|----|----|----|----|------|------|------|----|----|----|----|----|----|----|----|-----|---------|---------|

| S2 S1 S0 Sy ( | SA SA SA<br>0 1 2 | Sy | FC<br>0 | FC F | C Sy | RA<br>0 | RA<br>1 | RA<br>2 | Sy | RA<br>3 | RA<br>4 | RA<br>5 | Sy | RA<br>6 | RA<br>7 | D0 | Sy | D1 | D2 | D3   | Sy   | D4   | D5 | D6 | Sy | D7 | C2 | C1 | Sy | C0 | RC  | RD<br>1 | RD<br>2 |

| 0 1 0 1 0     | 0 1 0             | 1  | 1       | 0    | ) 1  | 0       | 0       | 0       | 1  | 0       | 0       | 0       | 1  | 1       | 0       | 0  | 1  | 1  | 0  | 0    | 1    | 1    | 0  | 0  | 1  | 0  | 0  | 0  | 1  | 0  | 1E1 | 76      | 12      |

Figure 11. PSI5 programming mode write register command and response format

Figure 12 is an example PSI5 programming mode command and response.

Figure 12. PSI5 programming mode command and response example

# 6 User OTP array programming via PSI5 programming mode

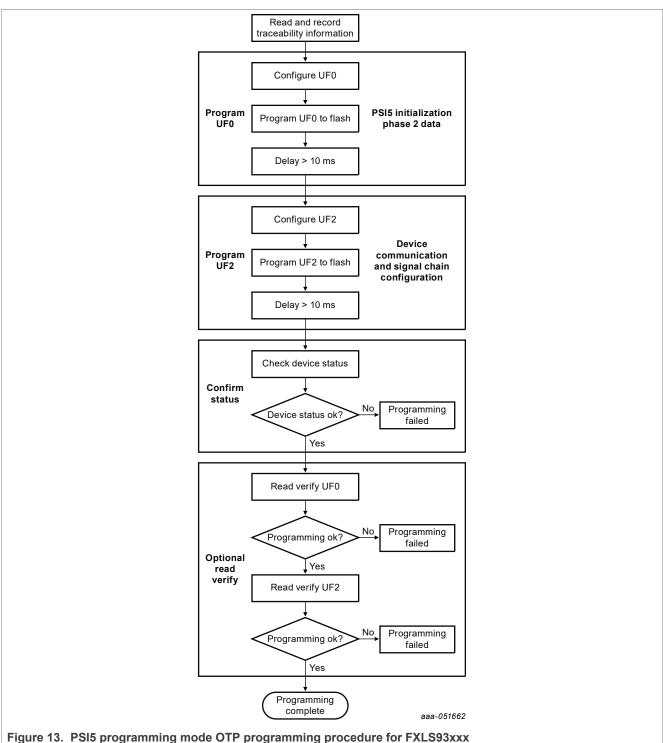

Figure 13 shows an overview of the User OTP array programming procedure. Each procedure block is covered by a separate subsection.

AN13761 Application note

Note that in the examples, some register writes to the value 0x00 are included for completeness. If a desired register value is 0x00, the write command need not be executed.

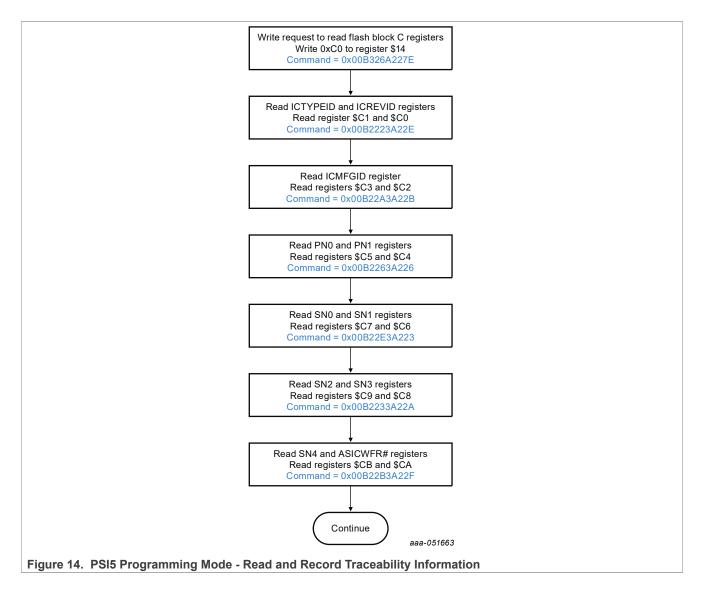

## 6.1 Optional read and record traceability information

Prior to programming the OTP of the device, the user can optionally read and record the device level traceability information, and confirm that the device part number is correct.

## **NXP Semiconductors**

# AN13761

#### PSI5 programming mode procedures for FXLS9xxxx sensors

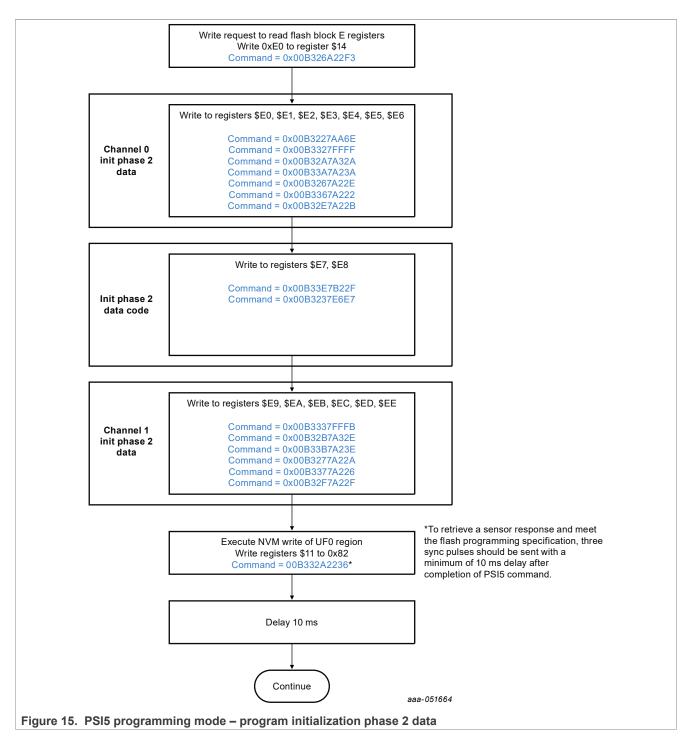

### 6.2 Program UF0: PSI5 initialization phase 2 data

The UF0 block of memory includes fifteen 8-bit user programmable registers from address \$E0 to \$EE that map to the PSI5 Initialization Phase two transmission data. The data mapping to initialization phase two data fields is shown in <u>Table 8</u>.

| Table 8. | UF0 register to | <b>PSI5</b> initialization | phase 2 data | field mapping |

|----------|-----------------|----------------------------|--------------|---------------|

|          |                 |                            | p            |               |

| L       | ocation    |                            |                                                                                                |         | В | lit                     |                      |                                 |   |  |  |  |

|---------|------------|----------------------------|------------------------------------------------------------------------------------------------|---------|---|-------------------------|----------------------|---------------------------------|---|--|--|--|

| Address | Register   | 7                          | 6                                                                                              | 5       | 4 | 3                       | 2                    | 1                               | 0 |  |  |  |

| \$E0    | USERDATA_0 |                            | Channel 1 F1:D1                                                                                |         |   |                         | Channel              | 0 F1:D1                         | 1 |  |  |  |

| \$E1    | USERDATA_1 | 1 Channel 0 F3:D5 Channel  |                                                                                                |         |   |                         |                      | Channel 0 F3:D5 Channel 0 F3:D4 |   |  |  |  |

| \$E2    | USERDATA_2 |                            | Channel 0 F4:D7                                                                                |         |   | Channel 0 F4:D7 Channel |                      |                                 |   |  |  |  |

| \$E3    | USERDATA_3 |                            | Channel                                                                                        | 0 F5:D8 |   |                         |                      |                                 |   |  |  |  |

| \$E4    | USERDATA_4 | Channel 0 F6:D11 Channel 0 |                                                                                                |         |   |                         | 0 F6:D10             |                                 |   |  |  |  |

| \$E5    | USERDATA_5 |                            | Channel 0 F7:D13                                                                               |         |   |                         | Channel              | 0 F7:D12                        |   |  |  |  |

| N13761  | 1          | 1                          | All information provided in this document is subject to legal disclaimers. © 2023 NXP B.V. All |         |   |                         | V. All rights reserv |                                 |   |  |  |  |

### PSI5 programming mode procedures for FXLS9xxxx sensors

| L       | ocation     |        |                                 |             | В      | lit                                 |         |          |        |

|---------|-------------|--------|---------------------------------|-------------|--------|-------------------------------------|---------|----------|--------|

| Address | Register    | 7      | 6                               | 5           | 4      | 3                                   | 2       | 1        | 0      |

| \$E6    | USERDATA_6  |        | Channel                         | 0 F9:D32    |        | Channel 0 F7:D14                    |         |          |        |

| \$E7    | USERDATA_7  | Channe | l 0 F8:D16 =                    | = Channel 1 | F8:D16 | Channel 0 F8:D15 = Channel 1 F8:D15 |         |          | F8:D15 |

| \$E8    | USERDATA_8  | Channe | l 0 F8:D18 =                    | = Channel 1 | F8:D18 | Channel 0 F8:D17 = Channel 1 F8:D17 |         |          | F8:D17 |

| \$E9    | USERDATA_9  |        | Channel 1 F3:D5 Channel 1 F3:D4 |             |        |                                     |         |          |        |

| \$EA    | USERDATA_A  |        | Channel                         | 1 F4:D7     |        |                                     | Channel | 1 F4:D6  |        |

| \$EB    | USERDATA_B  |        | Channel                         | 1 F5:D9     |        |                                     | Channel | 1 F5:D8  |        |

| \$EC    | USERDATA_C  |        | Channel                         | 1 F6:D11    |        |                                     | Channel | 1 F6:D10 |        |

| \$ED    | USERDATA_D  |        | Channel                         | 1 F7:D13    |        |                                     | Channel | 1 F7:D12 |        |

| \$EE    | USERDATA_E  |        | Channel                         | 1 F9:D32    |        | Channel 1 F9:D14                    |         |          |        |

| Facto   | ory Default | 0      | 0                               | 0           | 0      | 0 0 0 0                             |         |          | 0      |

Table 8. UF0 register to PSI5 initialization phase 2 data field mapping...continued

Figure 15 sets the PSI5 Initialization phase two data as shown in Table 9.

Table 9. Example PSI5 initialization phase 2 data

| Channel | PSI5 Field ID# | PSI5 Nibble ID # | Description                                                | Value         | Register               |

|---------|----------------|------------------|------------------------------------------------------------|---------------|------------------------|

|         | F1             | D1               | Protocol Revision 1.3                                      | 0x4           | E0[3:0]                |

|         | F2             | D2               | Number of Data Blocks = 32                                 | 0x2           | N/A                    |

|         | F2             | D3               | Number of Data Blocks = 32                                 | 0x0           | N/A                    |

|         | F3             | D4               | 0xFF Supplier Code                                         | 0xF           | E1[3:0]                |

|         | F3             | D5               | 0xFF Supplier Code                                         | 0xF           | E1[7:4]                |

|         | E4             | D6               | High g Sensor                                              | 0x0           | E2[3:0]                |

|         | F4             | D7               | High g Sensor                                              | 0x1           | E2[7:4]                |

|         | <b>FC</b>      | D8               | 120 g Sensor                                               | 0x0           | E3[3:0]                |

| 0       | F5             | D9               | 120 g Sensor                                               | 0x8           | E3[7:4]                |

| 0       | F6             | D10              | Sensor Specific Information = 0x0                          | 0x0           | E4[3:0]                |

|         | FO             | D11              | Sensor Specific Information = 0x0                          | 0x0           | E4[7:4]                |

|         |                | D12              | Sensor Specific Information = 0x0                          | 0x0           | E5[3:0]                |

|         | F7             | D13              | Sensor Specific Information = 0x0                          | 0x0           | E5[7:4]                |

|         |                | D14              | Sensor Specific Information = 0x0                          | 0x0           | E6[3:0]                |

|         |                | D15              | Date Code = April 22, 2016                                 | 0x2           | E7[3:0]                |

|         | F8             | D16              | Date Code = April 22, 2016                                 | 0x0           | E7[7:4]                |

|         | ГО             | D17              | Date Code = April 22, 2016                                 | 0x9           | E8[3:0]                |

|         |                | D18              | Date Code = April 22, 2016                                 | 0x6           | E8[7:4]                |

|         | F1             | D1               | Protocol Revision 1.3                                      | 0x4           | E0[7:4]                |

| 4       | F2             | D2               | Number of Data Blocks = 32                                 | 0x2           | N/A                    |

| 1       |                | D3               | Number of Data Blocks = 32                                 | 0x0           | N/A                    |

|         | F3             | D4               | 0xFF Supplier Code                                         | 0xF           | E9[3:0]                |

| 13761   | •              | All information  | provided in this document is subject to legal disclaimers. | © 2023 NXP B. | V. All rights reserved |

**Application note**

| Channel | PSI5 Field ID# | PSI5 Nibble ID # | Description                       | Value | Register |

|---------|----------------|------------------|-----------------------------------|-------|----------|

|         |                | D5               | 0xFF Supplier Code                | 0xF   | E9[7:4]  |

|         | F4             | D6               | High g Sensor                     | 0x0   | EA[3:0]  |

|         | F4             | D7               | High g Sensor                     | 0x1   | EA[7:4]  |

|         | F5             | D8               | 120 g Sensor                      | 0x0   | EB[3:0]  |

|         | FJ             | D9               | 120 g Sensor                      | 0x8   | EB[7:4]  |

|         | F6             | D10              | Sensor Specific Information = 0x0 | 0x0   | EC[3:0]  |

|         | FO             | D11              | Sensor Specific Information = 0x0 | 0x0   | EC[7:4]  |

|         |                | D12              | Sensor Specific Information = 0x0 | 0x0   | ED[3:0]  |

|         | F7             | D13              | Sensor Specific Information = 0x0 | 0x0   | ED[7:4]  |

|         |                | D14              | Sensor Specific Information = 0x0 | 0x0   | EE[3:0]  |

|         |                | D15              | Date Code = April 22, 2016        | 0x2   | E7[3:0]  |

|         | F8             | D16              | Date Code = April 22, 2016        | 0x0   | E7[7:4]  |

|         | FO             | D17              | Date Code = April 22, 2016        | 0x9   | E8[3:0]  |

|         |                | D18              | Date Code = April 22, 2016        | 0x6   | E8[7:4]  |

Table 9. Example PSI5 initialization phase 2 data...continued

## **NXP Semiconductors**

# AN13761

#### PSI5 programming mode procedures for FXLS9xxxx sensors

## 6.3 Program UF2: device configuration

The UF2 block of memory includes the user programmable communication and sensor signal chain configuration information.

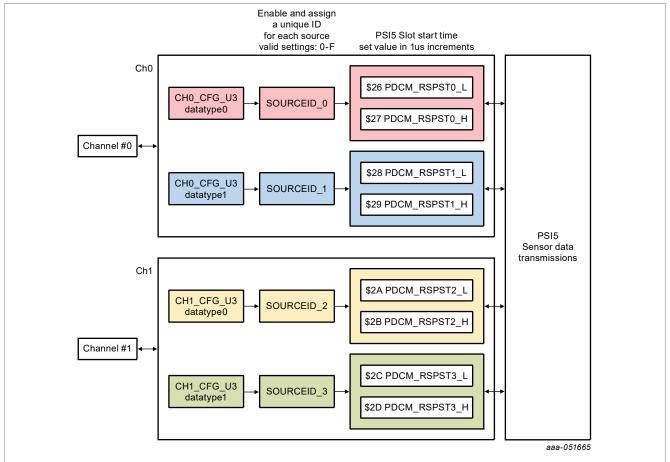

#### 6.3.1 Enable and Configure the Data Sources

Each channel of the FXLS93xxx devices is capable of two independently configurable data sources. Data source types include:

- · Acceleration data with offset cancellation enabled

- · Acceleration data with offset cancellation disabled (bypassed)

- Temperature sensor data

Figure 16 shows a pictorial mapping of the sources to their source identifiers and associated data.

Figure 16. Data source mapping diagram

PSI5 Daisy Chain mode or Asynchronous mode

In addition to data source transmission configuration, other PSI5 transmission configurations are possible by writes to the CHIPTIME register and the PSI5\_CFG register. Some possible configurations include:

PSI5 bit rate:

PSI5 error checking:

PSI5 Low-power mode

PSI5 Sync Pulse Blanking:

125 kbit/s or 189 kbit/s parity or 3-bit CRC Default set for 500 μs Sync pulse rate

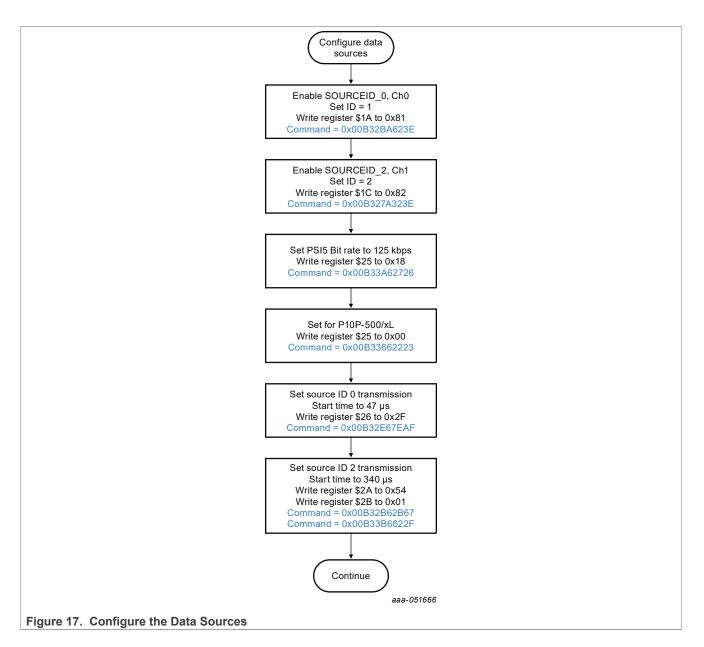

<u>Figure 17</u> shows one example configuration enabling acceleration data with offset cancellation enabled for each channel.

#### PSI5 programming mode procedures for FXLS9xxxx sensors

### 6.4 Configure the sensor signal chain

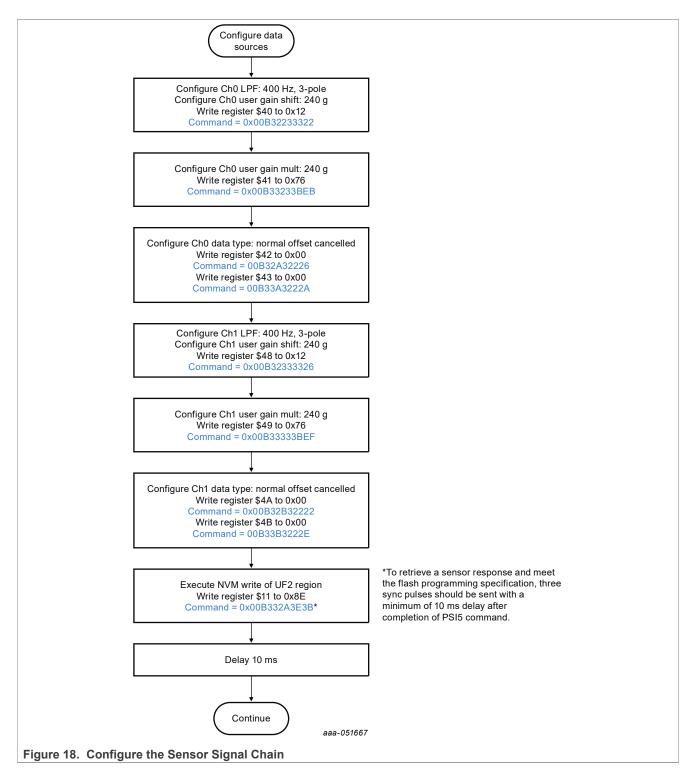

For specific use cases, the user can configure the sensor signal chain for each channel. <u>Figure 18</u> shows an example typical configuration for PSI5. <u>Section 6.4.1</u>, <u>Section 6.4.2</u>, and <u>Section 6.4.3</u> describe the user configurable options for the signal chain that apply to PSI5 transmissions.

#### PSI5 programming mode procedures for FXLS9xxxx sensors

### 6.4.1 Signal chain low-pass filter selection

A combinaton of the LPF bits and the SAMPLERATE bits in the CHx\_CFG\_U1 register selects the signal chain low-pass filter as shown in the datasheet. The LPF selection table is shown in <u>Table 10</u>.

|        |        |        |        |                     | Low-pass filter type |                  |

|--------|--------|--------|--------|---------------------|----------------------|------------------|

| LPF[3] | LPF[2] | LPF[1] | LPF[0] | SAMPLERATE = 00, 01 | SAMPLERATE = 10      | SAMPLERATE = 11  |

|        |        |        |        | 16 µs               | 32 µs                | 64 µs            |

| 0      | 0      | 0      | 0      | 400 Hz, 4-Pole      | 200 Hz, 4-Pole       | 100 Hz, 4-Pole   |

| 0      | 0      | 0      | 1      | 400 Hz, 3-Pole      | 200 Hz, 3-Pole       | 100 Hz, 3-Pole   |

| 0      | 0      | 1      | 0      | 400 Hz, 4-Pole      | 200 Hz, 4-Pole       | 100 Hz, 4-Pole   |

| 0      | 0      | 1      | 1      | 400 Hz, 3-Pole      | 200 Hz, 3-Pole       | 100 Hz, 3-Pole   |

| 0      | 1      | 0      | 0      | 325 Hz, 3-Pole      | 162.5 Hz, 3-Pole     | 81.25 Hz, 3-Pole |

| 0      | 1      | 0      | 1      | 370 Hz, 2-Pole      | 185 Hz, 2-Pole       | 92.5 Hz, 2-Pole  |

| 0      | 1      | 1      | 0      | 180 Hz, 2-Pole      | 90 Hz, 2-Pole        | 45 Hz, 2-Pole    |

| 0      | 1      | 1      | 1      | 100 Hz, 2-Pole      | 50 Hz, 2-Pole        | 25 Hz, 2-Pole    |

| 1      | 0      | 0      | 0      | 1500 Hz, 4-Pole     | 750 Hz, 4-Pole       | 375 Hz, 4-Pole   |

| 1      | 0      | 0      | 1      | 500 Hz, 3-Pole      | 250 Hz, 3-Pole       | 125 Hz, 3-Pole   |

| 1      | 0      | 1      | 0      | 800 Hz, 4-Pole      | 400 Hz, 4-Pole       | 200 Hz, 4-Pole   |

| 1      | 0      | 1      | 1      | 1200 Hz, 4-Pole     | 600 Hz, 4-Pole       | 300 Hz, 4-Pole   |

| 1      | 1      | 0      | 0      | 120 Hz, 3-Pole      | 60 Hz, 3-Pole        | 30 Hz, 3-Pole    |

| 1      | 1      | 0      | 1      | 20 kHz, 2-Pole      | 10 kHz, 2-Pole       | 5 kHz, 2-Pole    |

| 1      | 1      | 1      | 0      | 120 Hz, 2-Pole      | 60 Hz, 2-Pole        | 30 Hz, 2-Pole    |

| 1      | 1      | 1      | 1      | 50 Hz, 4-Pole       | 25 Hz, 4-Pole        | 12.5 Hz, 4-Pole  |

Table 10. Signal chain low-pass filter selection

### 6.4.2 Signal chain user gain selection

A combination of the U\_SNS\_SHIFT bits in the CHx\_CFG\_U1 register and the U\_SNS\_MULT bits in the CHx\_CFG\_U2 register selects the signal chain user gain. The equation and some example user range and sensitivities are included in the data sheet. The process and equations for determining the U\_SNS\_SHIFT and U\_SNS\_MULT settings from desired range and sensitivity values is listed below along with a typical high g PSI5 example.

- 1. Determine the overall sensitivity adjustment factor:

- Desired Typical User Range = ±240 g with 10-bit data

- Calculate Desired Sensitivity:

Sense<sub>Typical Desired</sub> =

$$\frac{2^9 \cdot 32}{Range_{Typical Desired}} = \frac{480}{240} = 2.00 LSB | g$$

• Calculate the required sensitivity adjustment for a High g device:

$$SENSE_{Adjust \ Total} = \frac{Sense_{Typical \ Desired}}{Sense_{Typical \ NXP \ Trim}} = \frac{2.00}{\left(\frac{10.9465}{4}\right)} = 0.7308$$

2. Determine the best U\_SNS\_SHIFT setting:

| Sense <sub>AdjustTotal</sub>           | U_SNS_SHIFT Gain | U_SNS_SHIFT Setting |

|----------------------------------------|------------------|---------------------|

| Sense <sub>AdjustTotal</sub> < 0.25    | Invalid Range    | Invalid Range       |

| $0.25 \leq Sense_{AdjustTotal} < 0.50$ | 0.25             | 00                  |

| $0.50 \leq Sense_{AdjustTotal} < 1.00$ | 0.50             | 01                  |

AN13761 Application note © 2023 NXP B.V. All rights reserved.

| Sense <sub>AdjustTotal</sub>           | U_SNS_SHIFT Gain | U_SNS_SHIFT Setting |

|----------------------------------------|------------------|---------------------|

| $1.00 \leq Sense_{AdjustTotal} < 2.00$ | 1.00             | 10                  |

| $2.00 \leq Sense_{AdjustTotal} < 4.00$ | 2.00             | 11                  |

| 4.00 ≤ Sense <sub>AdjustTotal</sub>    | Invalid Range    | Invalid Range       |

#### 3. Determine the U\_SNS\_MULT setting:

$$U SNS MULT = ROUND \left[ \left( \frac{Sense_{Typical Desired}}{Sense_{Typical NXP Trim^*U SNS SHIFT}} - 1 \right) \times 256 \right] = \left( \frac{0.7308}{0.50} - 1 \right) \times 256 = 118 decimal U_SNS_MULT = 0X76$$

#### 6.4.3 Signal chain data type configuration

Each source enabled (as described in <u>Section 6.3.1</u>) must have its data type configured. Datatype configuration is described in the data sheet. <u>Table 11</u> is a simplified table.

| CHx DATA | TYPEx[1:0] | Sensor data description                                 |

|----------|------------|---------------------------------------------------------|

| 0        | 0          | Offset Cancelled Data as Configured by the OC_FILT bits |

| 0        | 1          | Raw Data (No Offset Cancellation)                       |

| 1        | 0          | Temperature Sensor Data                                 |

| 1        | 1          | Temperature Sensor Data                                 |

#### Table 11. Simplified signal chain data type configuration

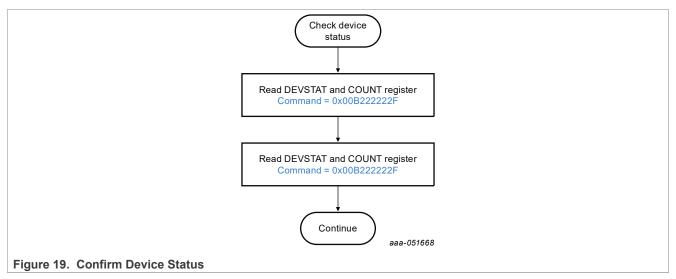

### 6.5 Confirm device status

Once programming is complete, the device reads back the new data from the OTP array and completes the memory verification. If the OTP write fails, the device status includes an error. Figure 19 shows the procedure to confirm the device status.

Note that self-test is not automatically run in PSI5 Programming Mode so the Chx\_ERR bits are set due to the ST\_INCMPLT bit being set.

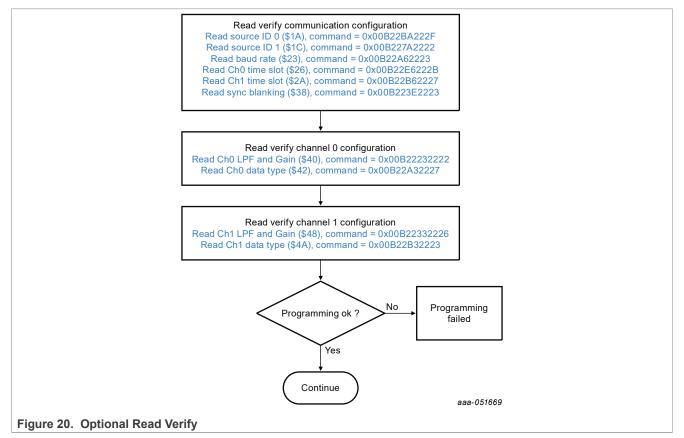

## 6.6 Optional read verify

If no memory errors are present after the OTP write and register values were verified after each register write during the programming process, then the programming process is complete. An additional read verify can be completed to confirm post OTP programming register values. <u>Figure 20</u> shows the read verify process.

### 6.7 Optional complete self-test

A self-test procedure will be added to the next revision of this application note.

# 7 Glossary

| Table 12. Glossary of terms |                                                                                                                                                                                                    |  |  |  |

|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Term                        | Definition                                                                                                                                                                                         |  |  |  |

| Analog self-test            | A method to test the acceleration signal chain by electrostatically deflecting the transducer proof mass and measuring the device output.                                                          |  |  |  |

| Digital self-test           | A method to test the digital portion of the acceleration signal chain by forcing a value or a sequence of values at the output of the analog-to-digital converter and measuring the device output. |  |  |  |

| DSP                         | Digital Signal Processing Block                                                                                                                                                                    |  |  |  |

| OTP                         | One Time Programmable Memory                                                                                                                                                                       |  |  |  |

| POR                         | Power-On Reset                                                                                                                                                                                     |  |  |  |

| PSI5                        | Peripheral Sensor Interface, fifth Generation. A single controller, multiple secondary communication interface that provides both secondary power and communication on a 2-wire bus.               |  |  |  |

AN13761 Application note

## 8 References

- [1] FXLS9xxxx, Dual-channel inertial sensor, data sheet, <u>https://www.nxp.com/docs/en/data-sheet/FXLS9xxxx.pdf</u>

- [2] FXLS9xxx0, Single channel inertial sensor, data sheet, <u>https://www.nxp.com/docs/en/data-sheet/FXLS9xxx0.pdf</u>

- [3] PSI5 Technical Specification Version 2.1, Dated October 8, 2012, https://www.psi5.org/specification

# 9 Revision history

| Table 13. Revision History |          |                                                                                                                                                                                                                                                                                                                  |  |  |

|----------------------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Rev                        | Date     | Description                                                                                                                                                                                                                                                                                                      |  |  |

| 1.1                        | 20231129 | <ul> <li><u>Section 6.2, Figure 15</u>, revised the image adding a note.</li> <li><u>Section 6.4</u>, Figure 18, revised the image adding a note.</li> <li><u>Section 9</u>, relocated the revision history from the start to the end of the document to conform to NXP's document content hierarchy.</li> </ul> |  |  |

| 1                          | 20230615 | Initial Release                                                                                                                                                                                                                                                                                                  |  |  |

# 10 Appendix

## 10.1 Example PSI5 Programming Mode Sequence with Timing

| Delta<br>Time<br>(ms) | Time<br>from<br>POR (ms) | Comma            | nd Type | Register<br>Addr | Register<br>Data | Comment                                                   | Full Command<br>(Hex) |

|-----------------------|--------------------------|------------------|---------|------------------|------------------|-----------------------------------------------------------|-----------------------|

| 6                     | 6                        | POR<br>Delay     | Delay   |                  |                  | POR Delay                                                 |                       |

| 7.75                  | 13.75                    | Startup<br>Delay | Delay   |                  |                  | Startup Delay pluse 31 Sync Pulses                        | FFFFFFF               |

| 3.6                   | 17.35                    | PME              | PME     |                  |                  |                                                           | ACF9                  |

| 11.25                 | 28.6                     | XLONG            | Write   | 1A               | 81               | Enable Channel 1 Data                                     | 00B32BA623E           |

| 11.25                 | 39.85                    | XLONG            | Write   | 1C               | 82               | Enable Channel 2 Data                                     | 00B327A323E           |

| 11.25                 | 51.1                     | XLONG            | Write   | 23               | 18               | Set baud rate to 125 kbit/s                               | 00B33A62726           |

| 11.25                 | 62.35                    | XLONG            | Write   | 26               | 2F               | Channel 0 Timeslot = 47 μs                                | 00B32E67EAF           |

| 11.25                 | 73.6                     | XLONG            | Write   | 27               | 00               | Channel 0 Timeslot = 47 μs                                | 00B33E62226           |

| 11.25                 | 84.85                    | XLONG            | Write   | 2A               | 54               | Channel 1 Timeslot = 340 μs                               | 00B32B62B67           |

| 11.25                 | 96.1                     | XLONG            | Write   | 2B               | 01               | Channel 1 Timeslot = 340 μs                               | 00B33B6622F           |

| 11.25                 | 107.35                   | XLONG            | Write   | 40               | 12               | Channel 0 400 Hz, 3-Pole LPF, 120 g High g                | 00B32233322           |

| 11.25                 | 118.6                    | XLONG            | Write   | 41               | 76               | Channel 0 400 Hz, 3-Pole LPF, 120 g High g                | 00B33233BEB           |

| 11.25                 | 129.85                   | XLONG            | Write   | 42               | 00               | Channel 0 Offset cancellation with 0.04 Hz, 1-Pole LPF    | 00B32A32226           |

| 11.25                 | 141.1                    | XLONG            | Write   | 43               | 00               | Channel 0 Offset cancellation with 0.04 Hz,<br>1-Pole LPF | 00B33A3222A           |

| 11.25                 | 152.35                   | XLONG            | Write   | 48               | 12               | Channel 1 400 Hz, 3-Pole LPF, 120 g High g                | 00B32333326           |

| 11.25                 | 163.6                    | XLONG            | Write   | 49               | 76               | Channel 1 400 Hz, 3-Pole LPF, 120 g High g                | 00B33333BEF           |

| 11.25                 | 174.85                   | XLONG            | Write   | 4A               | 00               | Channel 1 Offset cancellation with 0.04 Hz, 1-Pole LPF    | 00B32B32222           |

| Delta<br>Time<br>(ms) | Time<br>from<br>POR (ms) | Comma | nd Type | Register<br>Addr | Register<br>Data | Comment                                                | Full Command<br>(Hex) |

|-----------------------|--------------------------|-------|---------|------------------|------------------|--------------------------------------------------------|-----------------------|

| 11.25                 | 186.1                    | XLONG | Write   | 4B               | 00               | Channel 1 Offset cancellation with 0.04 Hz, 1-Pole LPF | 00B33B3222E           |

| 11.25                 | 197.35                   | XLONG | Write   | 14               | E0               | Enable writes to the PSI5 Init Phase 2 Data Section    | 00B326A22F3           |

| 11.25                 | 208.6                    | XLONG | Write   | E0               | 44               | Protocol = V1.3                                        | 00B3227AA6E           |

| 11.25                 | 219.85                   | XLONG | Write   | E1               | FF               | 0xFF Supplier Code                                     | 00B3327FFFF           |

| 11.25                 | 231.1                    | XLONG | Write   | E2               | 10               | High g Sensor                                          | 00B32A7A32A           |

| 11.25                 | 242.35                   | XLONG | Write   | E3               | 80               |                                                        | 00B33A7A23A           |

| 11.25                 | 253.6                    | XLONG | Write   | E4               | 00               |                                                        | 00B3267A22E           |

| 11.25                 | 264.85                   | XLONG | Write   | E5               | 00               |                                                        | 00B3367A222           |

| 11.25                 | 276.1                    | XLONG | Write   | E6               | 00               |                                                        | 00B32E7A22B           |

| 11.25                 | 287.35                   | XLONG | Write   | E7               | 02               | Set Data Code: April 22, 2016                          | 00B33E7B22F           |

| 11.25                 | 298.6                    | XLONG | Write   | E8               | 69               | Set Data Code: April 22, 2016                          | 00B3237E6E7           |

| 11.25                 | 309.85                   | XLONG | Write   | E9               | FF               | 0xFF Supplier Code                                     | 00B3337FFFB           |

| 11.25                 | 321.1                    | XLONG | Write   | EA               | 10               | High g Sensor                                          | 00B32B7A32E           |

| 11.25                 | 332.35                   | XLONG | Write   | EB               | 80               | 120 g Sensor                                           | 00B33B7A23E           |

| 11.25                 | 343.6                    | XLONG | Write   | EC               | 00               |                                                        | 00B3277A22A           |

| 11.25                 | 354.85                   | XLONG | Write   | ED               | 00               |                                                        | 00B3377A226           |

| 11.25                 | 366.1                    | XLONG | Write   | EE               | 00               |                                                        | 00B32F7A22F           |

| 11.25                 | 377.35                   | XLONG | Write   | 11               | 80               | Write the PSI5 Initialization Phase 2 data to<br>OTP   | 00B332A2236           |

| 8.75                  | 386.1                    | Delay | Delay   |                  |                  | Delay 10 ms                                            |                       |

| 11.25                 | 397.35                   | XLONG | Write   | 11               | 8E               | Write the Configuration Information to OTP             | 00B332A3E3B           |

| 8.75                  | 406.1                    | Delay | Delay   |                  |                  | Delay 10 ms                                            |                       |

| 11.25                 | 417.35                   | XLONG | Read    | 00               | 00               | Check Status                                           | 00B222222F            |

| 11.25                 | 428.6                    | XLONG | Read    | 00               | 00               | Check Status                                           | 00B222222F            |

## 10.2 PSI5 3-Bit CRC Calculation Examples

### 10.2.1 3-Bit CRC

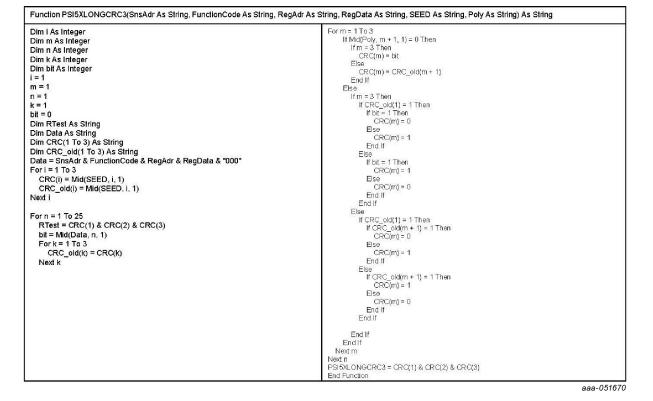

Figure 21 shows some example visual basic to calculate the PSI5 XLONG 3-bit CRC.

- Function PSI5XLONGCRC3(SnsAdr As String, FunctionCode As String, RegAdr As String, RegData As String, SEED As String, Poly As String) As String

- The data is composed of the following concatenated fields:

- 3-Bit Reversed SnsAdr 100

- 3-Bit Reversed FunctionCode: 100

- 8-Bit Reversed RegAdr: 0x40 0000 0010

- 8-Bit Reversed RegData: 0x12 0100 1000

- Example: Command = 100 100 0000 0010 0100 1000

- Example with Start and Sync Bits Command = 010 1 100 1 100 1 000 1 000 1 100 1 100 1 100 1 000 1 0

- Poly is the 4-bit CRC polynomial in binary

- Example: Polynomial =  $X^3 + X + 1$  Poly = 1011

SEED is the 3-bit CRC Initial value in binary Example: Seed = 0 x 7 SEED = 111

#### In this example, the CRC = 0x0.

Figure 21. PSI5 XLONG, 3-Bit CRC Visual Basic

#### PSI5 programming mode procedures for FXLS9xxxx sensors

# Legal information

## Definitions

**Draft** — A draft status on a document indicates that the content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included in a draft version of a document and shall have no liability for the consequences of use of such information.

## Disclaimers

Limited warranty and liability — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. NXP Semiconductors takes no responsibility for the content in this document if provided by an information source outside of NXP Semiconductors.

In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.

Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Terms and conditions of commercial sale of NXP Semiconductors.

**Right to make changes** — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Customers are responsible for the design and operation of their applications and products using NXP Semiconductors products, and NXP Semiconductors accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the NXP Semiconductors product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products.

NXP Semiconductors does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using NXP Semiconductors products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer(s). NXP does not accept any liability in this respect. Terms and conditions of commercial sale — NXP Semiconductors products are sold subject to the general terms and conditions of commercial sale, as published at https://www.nxp.com/profile/terms, unless otherwise agreed in a valid written individual agreement. In case an individual agreement is concluded only the terms and conditions of the respective agreement shall apply. NXP Semiconductors hereby expressly objects to applying the customer's general terms and conditions with regard to the purchase of NXP Semiconductors products by customer.

Suitability for use in automotive applications - This NXP product has been qualified for use in automotive applications. If this product is used by customer in the development of, or for incorporation into, products or services (a) used in safety critical applications or (b) in which failure could lead to death, personal injury, or severe physical or environmental damage (such products and services hereinafter referred to as "Critical Applications"), then customer makes the ultimate design decisions regarding its products and is solely responsible for compliance with all legal, regulatory, safety, and security related requirements concerning its products, regardless of any information or support that may be provided by NXP. As such, customer assumes all risk related to use of any products in Critical Applications and NXP and its suppliers shall not be liable for any such use by customer. Accordingly, customer will indemnify and hold NXP harmless from any claims, liabilities, damages and associated costs and expenses (including attorneys' fees) that NXP may incur related to customer's incorporation of any product in a Critical Application.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.

**Translations** — A non-English (translated) version of a document, including the legal information in that document, is for reference only. The English version shall prevail in case of any discrepancy between the translated and English versions.

Security — Customer understands that all NXP products may be subject to unidentified vulnerabilities or may support established security standards or specifications with known limitations. Customer is responsible for the design and operation of its applications and products throughout their lifecycles to reduce the effect of these vulnerabilities on customer's applications and products. Customer's responsibility also extends to other open and/or proprietary technologies supported by NXP products for use in customer's applications. NXP accepts no liability for any vulnerability. Customer should regularly check security updates from NXP and follow up appropriately. Customer shall select products with security features that best meet rules, regulations, and standards of the intended application and make the ultimate design decisions regarding its products and is solely responsible for compliance with all legal, regulatory, and security related requirements concerning its products, regardless of any information or support that may be provided by NXP.

NXP has a Product Security Incident Response Team (PSIRT) (reachable at <u>PSIRT@nxp.com</u>) that manages the investigation, reporting, and solution release to security vulnerabilities of NXP products.

**NXP B.V.** — NXP B.V. is not an operating company and it does not distribute or sell products.

## Trademarks

Notice: All referenced brands, product names, service names, and trademarks are the property of their respective owners. **NXP** — wordmark and logo are trademarks of NXP B.V.

## PSI5 programming mode procedures for FXLS9xxxx sensors

# **Tables**

| Tab. 1. | Applicable parts2                     |

|---------|---------------------------------------|

| Tab. 2. | PSI5 OTP Programming of a PSI5        |

|         | application device2                   |

| Tab. 3. | PSI5 parameters and values4           |

| Tab. 4. | PSI5 programming mode entry command   |

|         | parameters and values6                |

| Tab. 5. | PSI5 programming mode entry settings6 |

| Tab. 6. | PSI5 programming register read        |

|         | parameters and values9                |

# **Figures**

| Fig. 1.  | Application schematic                |   |

|----------|--------------------------------------|---|

| Fig. 2.  | Programming Voltage Supply Ramp      | 4 |

| Fig. 3.  | PSI5 Programming Mode Short Command  |   |

|          | and Response Format                  | 4 |

| Fig. 4.  | PSI5 Programming Mode Extra Long     |   |

|          | Command and Response Format          | 5 |

| Fig. 5.  | Power On PSI5 Programming Mode       |   |

|          | Communication Delay                  | 5 |

| Fig. 6.  | PSI5 Programming Mode Entry Start    |   |

| -        | Condition, 31 Sync Pulses            | 6 |

| Fig. 7.  | PSI5 Programming Mode Entry Command  | 7 |

| Fig. 8.  | PSI5 Programming Mode Entry Response | 8 |

| Fig. 9.  | PSI5 Programming Mode Command Start  |   |

| C C      | Condition, 6 nSync Bits              | 9 |

| Fig. 10. | PSI5 programming mode read register  |   |

| č        | command and response format          | 9 |

| PSI5 programming register write             |                                                                                                                                                                                                                                                             |

|---------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| parameters and values                       | 10                                                                                                                                                                                                                                                          |

| UF0 register to PSI5 initialization phase 2 |                                                                                                                                                                                                                                                             |

| data field mapping                          | 12                                                                                                                                                                                                                                                          |

| Example PSI5 initialization phase 2 data    | 13                                                                                                                                                                                                                                                          |

| Signal chain low-pass filter selection      | 19                                                                                                                                                                                                                                                          |

| Simplified signal chain data type           |                                                                                                                                                                                                                                                             |

| configuration                               | 20                                                                                                                                                                                                                                                          |

| Glossary of terms                           | 21                                                                                                                                                                                                                                                          |

| Revision History                            | 22                                                                                                                                                                                                                                                          |

|                                             | parameters and values<br>UF0 register to PSI5 initialization phase 2<br>data field mapping<br>Example PSI5 initialization phase 2 data<br>Signal chain low-pass filter selection<br>Simplified signal chain data type<br>configuration<br>Glossary of terms |

| PSI5 programming mode write register  |

|---------------------------------------|

| command and response format 10        |

| PSI5 programming mode command and     |

| response example10                    |

| PSI5 programming mode OTP             |

| programming procedure for FXLS93xxx11 |

| PSI5 Programming Mode - Read and      |

| Record Traceability Information12     |

| PSI5 programming mode – program       |

| initialization phase 2 data15         |

| Data source mapping diagram16         |

| Configure the Data Sources17          |

| Configure the Sensor Signal Chain     |

| Confirm Device Status 20              |

| Optional Read Verify21                |

| PSI5 XLONG, 3-Bit CRC Visual Basic 24 |

|                                       |

#### PSI5 programming mode procedures for FXLS9xxxx sensors

## Contents

| 1      | Introduction2                            |

|--------|------------------------------------------|

| 2      | Applicable parts2                        |

| 3      | Application schematic and device         |

|        | connections2                             |

| 4      | Device power restrictions3               |

| 5      | Bidirectional communication via PSI5     |

|        | programming mode4                        |

| 5.1    | Power on PSI5 programming mode           |

|        | communication delay5                     |

| 5.2    | PSI5 programming mode entry start        |

|        | condition5                               |

| 5.3    | PSI5 programming mode entry command6     |

| 5.4    | PSI5 programming mode normal command     |

|        | start condition8                         |

| 5.5    | PSI5 programming mode normal             |

|        | commands and responses9                  |

| 6      | User OTP array programming via PSI5      |

|        | programming mode10                       |

| 6.1    | Optional read and record traceability    |

|        | information11                            |

| 6.2    | Program UF0: PSI5 initialization phase 2 |

|        | data12                                   |

| 6.3    | Program UF2: device configuration 15     |

| 6.3.1  | Enable and Configure the Data Sources 16 |

| 6.4    | Configure the sensor signal chain 17     |

| 6.4.1  | Signal chain low-pass filter selection18 |

| 6.4.2  | Signal chain user gain selection19       |

| 6.4.3  | Signal chain data type configuration20   |

| 6.5    | Confirm device status20                  |

| 6.6    | Optional read verify21                   |

| 6.7    | Optional complete self-test21            |

| 7      | Glossary21                               |

| 8      | References22                             |

| 9      | Revision history22                       |

| 10     | Appendix22                               |

| 10.1   | Example PSI5 Programming Mode            |

|        | Sequence with Timing22                   |

| 10.2   | PSI5 3-Bit CRC Calculation Examples23    |

| 10.2.1 | 3-Bit CRC 23                             |

|        | Legal information25                      |

|        |                                          |

Please be aware that important notices concerning this document and the product(s) described herein, have been included in section 'Legal information'.

© 2023 NXP B.V.

All rights reserved.

For more information, please visit: https://www.nxp.com